# Hardware developments V E-CAM Deliverable 7.9

E-CAM Deliverable 7.9 Deliverable Type: Report Delivered in July, 2020

E-CAM The European Centre of Excellence for Software, Training and Consultancy in Simulation and Modelling

Funded by the European Union under grant agreement 676531

| Project and Deliverable Information |                                                                                   |  |  |  |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Project Title                       | E-CAM: An e-infrastructure for software, training and discussion in simulation    |  |  |  |  |  |  |

|                                     | and modelling                                                                     |  |  |  |  |  |  |

| Project Ref.                        | Grant Agreement 676531                                                            |  |  |  |  |  |  |

| Project Website                     | https://www.e-cam2020.eu                                                          |  |  |  |  |  |  |

| EC Project Officer                  | Juan Pelegrín                                                                     |  |  |  |  |  |  |

| Deliverable ID                      | D7.9                                                                              |  |  |  |  |  |  |

| Deliverable Nature                  | Report                                                                            |  |  |  |  |  |  |

| Dissemination Level                 | Public                                                                            |  |  |  |  |  |  |

| Contractual Date of Delivery        | Project Month 54(31 <sup>st</sup> March, 2020)                                    |  |  |  |  |  |  |

| Actual Date of Delivery             | 6 <sup>th</sup> July, 2020                                                        |  |  |  |  |  |  |

| Description of Deliverable          | Update on "Hardware Developments IV" (Deliverable 7.7) which covers:              |  |  |  |  |  |  |

|                                     | - Report on hardware developments that will affect the scientific areas of inter- |  |  |  |  |  |  |

|                                     | est to E-CAM and detailed feedback to the project software developers (STFC);     |  |  |  |  |  |  |

|                                     | - discussion of project software needs with hardware and software vendors,        |  |  |  |  |  |  |

|                                     | completion of survey of what is already available for particular hardware plat-   |  |  |  |  |  |  |

|                                     | forms (FR-IDF); and,                                                              |  |  |  |  |  |  |

|                                     | - detailed output from direct face-to-face session between the project end-       |  |  |  |  |  |  |

|                                     | users, developers and hardware vendors (ICHEC).                                   |  |  |  |  |  |  |

# Project and Deliverable Information

# **Document Control Information**

|                                     | Title:            | Hardware developments V                                                  |  |  |  |  |  |

|-------------------------------------|-------------------|--------------------------------------------------------------------------|--|--|--|--|--|

|                                     | ID:               | D7.9                                                                     |  |  |  |  |  |

| Desurrent                           | Version:          | As of July, 2020                                                         |  |  |  |  |  |

| Document                            | Status:           | Accepted by WP leader                                                    |  |  |  |  |  |

|                                     | Available at:     | https://www.e-cam2020.eu/deliverables                                    |  |  |  |  |  |

|                                     | Document history: | Internal Project Management Link                                         |  |  |  |  |  |

| Review                              | Review Status:    | Reviewed                                                                 |  |  |  |  |  |

|                                     | Written by:       | Alan Ó Cais(JSC)                                                         |  |  |  |  |  |

| Authorship                          | Contributors:     | Christopher Werner (ICHEC), Simon Wong (ICHEC), Padraig Ó Conbhuí        |  |  |  |  |  |

| Autionship                          |                   | (ICHEC), Alan Ó Cais (JSC), Jony Castagna (STFC), Godehard Sutmann (JSC) |  |  |  |  |  |

|                                     | Reviewed by:      | Luke Drury (NUID UCD) and Jony Castagna (STFC)                           |  |  |  |  |  |

| Approved by: Godehard Sutmann (JSC) |                   |                                                                          |  |  |  |  |  |

# **Document Keywords**

Keywords: E-CAM, HPC, Hardware, CECAM, Materials

6<sup>th</sup> July, 2020

**Disclaimer**: This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements.

**Copyright notices**: This deliverable was co-ordinated by Alan Ó Cais<sup>1</sup> (JSC) on behalf of the E-CAM consortium with contributions from Christopher Werner (ICHEC), Simon Wong (ICHEC), Padraig Ó Conbhuí (ICHEC), Alan Ó Cais (JSC), Jony Castagna (STFC), Godehard Sutmann (JSC). This work is licensed under the Creative Commons Attribution 4.0 International License. To view a copy of this license, visit:

http://creativecommons.org/licenses/by/4.0

<sup>1</sup>a.ocais@fz-juelich.de

# Contents

**Executive Summary**

| 1 | Introduction         1.1       Scope of the deliverable         1.1.1       Target audience         1.2       Extent of the update to Hardware Developments IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>3</b><br>3<br>3<br>3                                                                                                                                                                                                          |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Hardware Developments         2.1         Influential factors         2.1.1       General outlook         2.1.2       The impact of power considerations         2.1.3       The impact of Deep Learning         2.1.4       Intellectual Property origin         2.1.5       Notable Hardware Developments         2.2.1       European Processor Initiative         2.2.2       Intel         2.2.3       AMD         2.2.4       NVIDIA         2.2.5       ARM         2.2.6       EuroEXA         2.2.7       Complex I/O layers         2.2.8       Memory Hierarchy         2.2.9       Feedback for software developers         2.3.1       EuroHPC         2.3.3       Feedback for software developers | <b>4</b><br><b>4</b><br><b>4</b><br><b>5</b><br><b>5</b><br><b>5</b><br><b>6</b><br><b>6</b><br><b>6</b><br><b>7</b><br><b>7</b><br><b>7</b><br><b>8</b><br><b>8</b><br><b>9</b><br><b>9</b><br><b>9</b><br><b>9</b><br><b>9</b> |

| 3 | Software Needs         3.1       Software needs as collected by the E-CAM Software Survey         3.1.1       Feedback for hardware and software vendors         3.2       Programming Paradigms         3.2.1       C++17         3.2.2       Fortran 2018         3.2.3       The (potential) role of Python         3.2.4       Open Standards         3.2.5       Vendor Specific Libraries         3.2.6       Runtime System Approaches         3.2.7       Open Science                                                                                                                                                                                                                                   | <pre>11 11 13 13 13 13 14 14 15 16 17 17</pre>                                                                                                                                                                                   |

| 4 | <ul> <li>4.1 Outcomes and key recommendations from the <i>E-CAM Extreme-Scale State-of-the-Art Workshop</i></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ol> <li>19</li> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> <li>23</li> <li>24</li> <li>25</li> </ol>                                                                                                           |

| 5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>26</b><br>26                                                                                                                                                                                                                  |

| A |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>28</b><br>28                                                                                                                                                                                                                  |

1

| c   |       |                                                                                              | ~~ |

|-----|-------|----------------------------------------------------------------------------------------------|----|

|     | A.2.9 | "Exascale challenges: the view from EoCoE" – Matthieu Haefele                                | 34 |

|     |       | "Exascale challenges: the view from NoMAD" – Claudia Draxl                                   |    |

|     |       | "Exascale challenges: the view from MaX" – Carlo Cavazzoni                                   | 32 |

|     |       | "POP – understanding applications and how to prepare for exascale" – Jesus Labarta           | 32 |

|     |       | mann                                                                                         | 31 |

|     | A.2.5 | "MP2C: Multiple-particle collision dynamics on massively parallel computers" – Godehard Sut- |    |

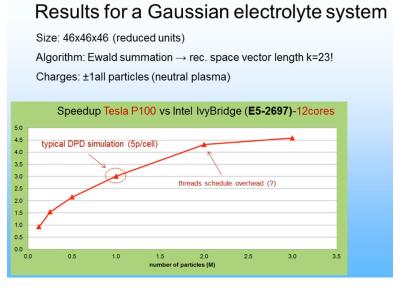

|     | A.2.4 | "Porting DL_MESO_DPD on GPUs" – Jony Castagna                                                | 31 |

|     |       | "PaPIM: A Code for (Quantum) Time Correlation Functions" – Momir Malis                       |    |

|     |       | "Scalability of Path Sampling Simulations" – David Swenson                                   |    |

|     |       |                                                                                              |    |

| A.2 |       | ale challenges in exploiting massive parallelism                                             |    |

|     |       | The Mont-Blanc projects                                                                      |    |

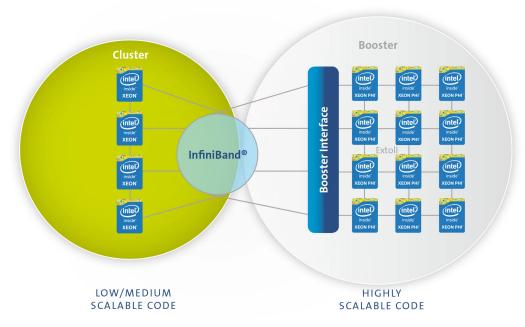

|     |       | The DEEP projects – overview of the architecture                                             |    |

|     |       |                                                                                              |    |

# References

# 36

# List of Figures

| 1  | Factors that will influence the challenges in HPC over the coming decade (©Eurolab4HPC) | 4  |

|----|-----------------------------------------------------------------------------------------|----|

| 2  | List of PRACE Resources (as of 2020) with associated hardware characteristics.          | 10 |

| 3  | Question: Who develops the software?                                                    | 11 |

| 4  | Question: The Programming Language used by the software.                                | 11 |

| 5  | Supported (parallel) software capabilities                                              | 11 |

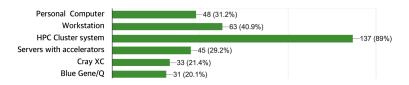

| 6  | Most common hardware used for generating publication-quality results                    | 12 |

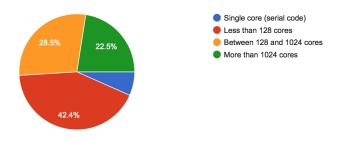

| 7  | Max number of cores used per run                                                        | 12 |

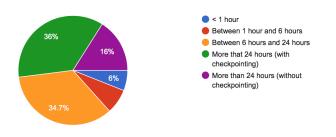

| 8  | Max number of hours used per run                                                        | 12 |

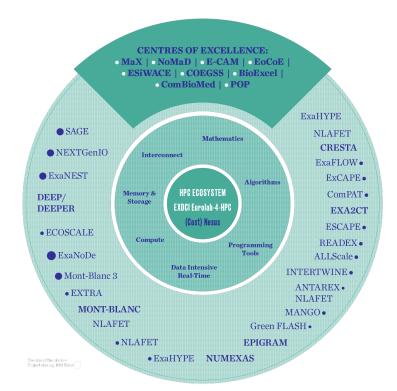

| 9  | The European HPC Technology Projects within the European HPC Eco-system.                | 22 |

| 10 | The DEEP hardware architecture.                                                         | 28 |

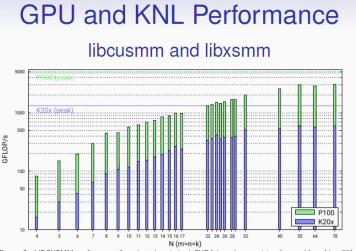

| 11 | CP2K Presentation: GPU and KNL Performance                                              | 30 |

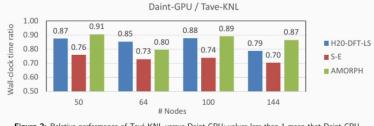

| 12 | DL_MESO: GPU porting results                                                            | 31 |

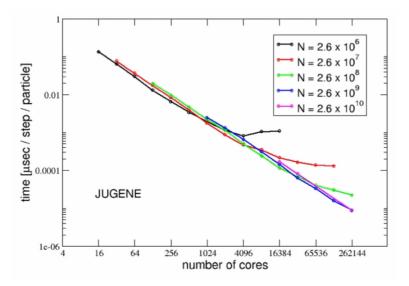

| 13 | MP2C scaling on JUGENE                                                                  | 32 |

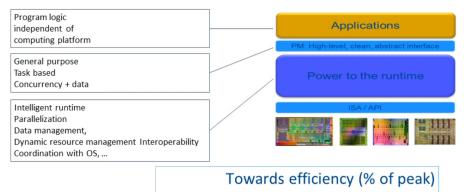

| 14 | POP: Different software layers                                                          | 33 |

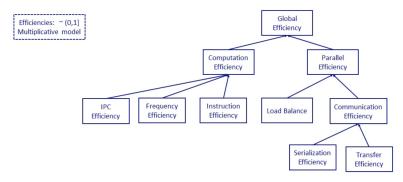

| 15 | Fundamental performance factors in evaluating performance                               | 33 |

| 16 | Overview of materials data and their structure                                          | 34 |

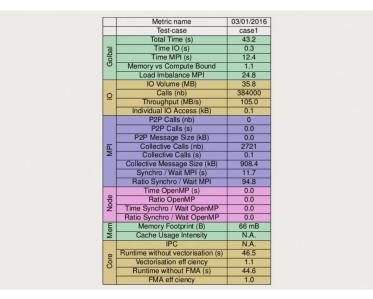

| 17 | EoCoE Performance metrics table                                                         | 34 |

# **Executive Summary**

The recommendations of this deliverable are targeted at the development community connected to E-CAM. We highlight the impact that immediate hardware developments are likely to have on the software applications of the E-CAM community. We also provide a set of recommendations to our user community with respect to how to prepare for, and deal with, these developments. Based on the perceived needs of our user community, this report is composed of 3 main parts, namely:

- *Hardware Developments* (Section 2) which provides a summarised update to Hardware Developments that we see as relevant to the E-CAM community in the 3-5 year horizon. In this section, roadmaps of HPC development, power considerations, hardware developments of particular significance are presented, as well as the current and expected availability of extreme-scale resources at the European level. Detailed feedback to E-CAM software developers is also given covering topics such as: using several development approaches such as CUDA, OpenACC, OpenMP, HIP and others to exploit the full power of GPUs, FPGAs and many-core architectures. It is fundamental to consider the several issues related the heterogeneity of exascale architectures, such as CPU-GPU bandwidth communication. The technologies described in this section are very likely to feature in any available European exascale technologies.

- *Software Needs* (Section 3) gives an update to the software needs of the project and what will be required of the software when targeting extreme-scale resources. In this section, an analysis of the ongoing "E-CAM Survey of Application Software" is provided. Feedback for hardware and software vendors is given, noting in particular that there is still a heavy reliance in the community on Fortran and support for this language will be essential on future systems for current workloads. A subset of possible programming paradigms are covered: C++17, Fortran 2018, several Open Standards (MPI/OpenMP/OpenACC/OpenCL) and runtime-system approaches (HPX/Kokkos/OmpSs/Charm++). For software developers, awareness of the latest standards and the status of their implementations are critical during application development as these new features exist to target the scalability challenges on modern systems. We provide a limited set of recommendations for people in E-CAM community who are embarking on a new software project: using MPI+OpenMP with their latest standards remains the safest bet with good performance and scalability achievable; you can prototype quickly using Python and leveraging the Python APIs to the libraries you need; using C++ with Python interfaces can help achieve maximal performance (and it helps that computer scientists seem to prefer C++ when creating innovative runtime systems).

- *Interactions between end-users, developers and vendors* (Section 4) describes the face-to-face discussions that have taken place between E-CAM developers, users and the hardware and software vendors. This section reflects the E-CAM Extreme-Scale State-of-the-Art Workshop held in Barcelona in June 2017, the Scoping Workshop *"Building the bridge between theories and software: SME as a boost for technology transfer in industrial simulative pipelines"* held in Genoa in 2018, as well as the interaction of the project with ETP4HPC, EuroHPC and EU hardware projects (in particular via the CoE coordination project FocusCoE). The European exascale roadmap, emerging hardware architectures relevant to exascale computing and exascale challenges in exploiting massive parallelism are reported in this section. Key outcome and recommendations include: E-CAM needs to develop niche activities to provide mutual benefit for both our industry partners and E-CAM's HPC oriented goals. We should provide a reliable software delivery mechanism between academic software developers and industrial partners. We also sought to increase the E-CAM community exposure to HPC technologies by organising a set of pilot projects covering High Throughput Computing (HTC), load-balancing and novel runtime technologies as well as a number of activities oriented towards deep learning.

Discussions are also realised with hardware/software vendors through our participation in the development of the ETP4HPC Strategic Research Agenda and our participation in the EuroHPC Working Group on User Requirements.

We conclude this document by putting it's findings in the context of a scientific area of E-CAM that is gaining growing attention and industrial appeal: multiscale modelling, which has huge potential in the E-CAM community for the computational study of structure formation and processes at mesoscopic length and time scales. When addressing multiple scales there are significant methodological challenges, including algorithm design for horizontal coupling of scales (where all scales are simulated at once) and mapping techniques for vertical coupling (distinct, but coupled, simulations at different scales, with each scale posing different simulation challenges).

The coupling of scales is necessarily complex and frequently requires an adaptive workflow (either internally through libraries, or externally through additional application codes) orchestrating a simulation across different scales that is highly susceptible to scalability issues, in particular load-balancing problems. This complexity quickly exposes the advantage of using, and contributing to, middle-layer libraries since they can be leveraged across the workflow and help to minimise the effort of adapting to new architectures (which becomes a *tuning* effort as opposed to a development effort). Eurolab4HPC has already indicated that there are several initiatives moving in this direction, and

that developing for current and future high-end architectures, as found in HPC centres, will require such a shift:

Manual optimization of the data layout, placement, and caching will become uneconomic and time consuming, and will, in any case, soon exceed the abilities of the best human programmers.

Nascent fields such as multiscale modelling which have scientific use cases that should map well to exascale resources would be wise to heed such advice.

# 1 Introduction

# 1.1 Scope of the deliverable

This deliverable is divided into 3 main parts, namely:

- Analysis of hardware developments expected in the 3-5 year horizon with feedback to software developers (Section 2);

- Survey of software and hardware currently used by the E-CAM community (and the level of parallelisation used). Analysis of software future needs and requirements with feedback to software developers, as well as hardware and software vendors (Section 3);

- Discussion of project software needs with hardware and software vendors, and detailed output from direct faceto-face session between the project end-users, developers and hardware vendors (Section 4).

## 1.1.1 Target audience

The recommendations of this deliverable are targeted at the development community connected to E-CAM. We highlight the impact that immediate hardware developments are likely to have on the software applications of the E-CAM community. We also provide a set of recommendations to our user community with respect to how to prepare for, and deal with, these developments.

In addition, our software survey, in particular, provides hardware and software vendors with valuable insight into the normal simulation software and practices of our user community.

# 1.2 Extent of the update to Hardware Developments IV

In E-CAM's *Hardware Developments IV* deliverable [1], we maintained a focus on the disruptive aspects of the hardware and software technologies that are most likely to impact the software development practices of the E-CAM community.

The current deliverable maintains a similar structure to the previous deliverable with updates to reflect the state of the art. Significant additions include

- the consideration of the "Eurolab4HPC Long-Term Vision on High-Performance Computing (2nd Edition)" in our analysis

- hardware updates from major vendors

- further details on the EuroHPC joint undertaking and the related hardware developments,

- discussions on how to deal with the I/O layer,

- the inclusion of the E-CAM Scoping Workshop entitled "Building the bridge between theories and software: SME as a boost for technology transfer in industrial simulative pipelines" (Section 4.2),

- the cultivation of machine learning expertise within the project, and the organisation of associated training events (Section 4.3),

- updates on relevant aspects of WP7 pilot projects.

Task 3 of WP7 involved interfacing the user-community with software developments and hardware vendors. We have provided 2 feedback sessions where the software developed within the project is presented to a combined audience of users and hardware vendors. The first was the Extreme-scale State-of-the-Art workshop (Section 4.1) held in RP2. The second of these is the Scoping Workshop mentioned above (Section 4.2), where the audience was primarily software as opposed to hardware vendors since E-CAM has recognised key role of SMEs that take academic concepts and prepare them for the marketplace.

# 2 Hardware Developments

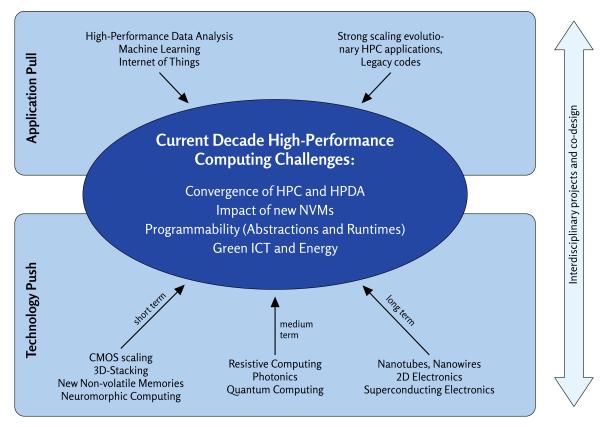

Figure 1: Factors that will influence the challenges in HPC over the coming decade (©Eurolab4HPC)

There are a number of different organisations and projects that are generating roadmaps about the current and future technologies that are (or may be in the future) available in the High Performance Computing (HPC) space. A summary table of which had been created by Eurolab-4-HPC for their report on the "Eurolab4HPC Long-Term Vision on High-Performance Computing (2nd Edition)", including summary input from projects such as PRACE, ETP4HPC, HiPEAC, BDVA and others.

The second edition Eurolab4HPC Vision was released in January 2020 but a summary graphic they created highlights the factors that influence this document (reproduced in Fig.1). In this section we will focus on a small subset of the content of these roadmaps (primarily from Eurolab4HPC and ETP4HPC) that are most likely to impact the target community of E-CAM in the 3-5 year horizon and likely beyond.

# 2.1 Influential factors

There are a number of economical factors that will have a strong influence on aspects of the hardware that will be realised in exascale machines. We discuss two here: the practical consideration of the power budget required to run such a resource and the market-led influence of deep learning on *commodity* hardware that can be leveraged.

# 2.1.1 General outlook

The current trend of HPC scaling based around floating point operations is expected to continue well beyond Exascale computers, however, the landscapes in which HPC is operating are changing. This is due to 3 main trends.

Firstly is the emergence of High Performance Data Analytics (HPDA) complementing simulation in scientific discovery and future HPC applications.

The second trend is the continued emergence of cloud computing and warehouse-scale computers, which aim at cost-effective data manipulation at previously unprecedented scales, which has led to fundamental breakthroughs as a result. Different algorithms are needed in data and cloud computing centres compared to traditional HPC applications and may not require the same computer structures.

The third trend arises from Deep Neural Networks (DNN) for back propagation learning of complex patterns. GPU accelerators are seen as very effective for this field, given support for 16-bit floating point and tensor processing units.

The overall trend and target is to develop systems that adapt more quickly to changing environments, more complex systems and this is expected to continue over the next decade.

## 2.1.2 The impact of power considerations

For the last decade, power and thermal management has been of high importance. The entire market focus has moved from achieving better performance through single-thread optimizations, e.g., speculative execution, towards simpler architectures that achieve better performance per watt, provided that vast parallelism exists. The HPC community, particularly at the higher end, focuses on the flops/watt metric since the running cost of high-end HPC systems are so significant. It is the potential power requirements of exa-scale systems that are the limiting factor (given currently available technologies). The practical outcome of this is the rise of accelerating co-processors and many-core systems. In the following sections we will mention such technologies in the context of relevant international exa-scale projects. The problem with the current two-pronged advance is that it is not always easy to develop parallel programs for these technologies and, moreover, those parallel programs are not always performance portable between each technology (particularly since FPGAs use a data-flow programming model), meaning that each time the architecture (or indeed the vendor) changes, the code may have to be rewritten. While there may be open standards available for each technology, each product currently has different preferred standards which are championed by the individual vendors (and therefore the best performing).

In general, we see a clear trend towards more complex systems, which is expected to continue over the next decade. These developments will significantly increase software complexity, demanding more and more intelligence across the programming environment, including compiler, run-time and tool intelligence driven by appropriate programming models. Manual optimisation of the data layout, placement, and caching will become uneconomic and time consuming, and will, in any case, most likely soon exceed the abilities of the best human programmers.

## 2.1.3 The impact of Deep Learning

Traditional machine learning uses handwritten feature extraction and modality-specific machine learning algorithms to label images or recognize voices. However, this method has several drawbacks in both time-to-solution and accuracy. Today's advanced deep neural networks use algorithms, big data, and the computational power of the GPU (and other technologies) to change this dynamic. Machines are now able to learn at a speed, accuracy, and scale that are driving true artificial intelligence and AI Computing.

Deep learning is used in the research community and in industry to help solve many big data problems such as computer vision, speech recognition, and natural language processing. Practical examples include:

- Vehicle, pedestrian and landmark identification for driver assistance

- Image recognition

- Speech recognition and translation

- Natural language processing

- Life sciences

The influence of Deep Learning on the market is significant with all major vendors of processors including accelerators having to accommodate workloads that are different from conventional HPC, e.g. support for massively parallel lower precision 32-bit floating point arithmetic, and integer arithmetic. Increasingly, we are seeing new processor designs that adopts a modular, chiplets approach where execution units specialised for different workloads can be integrated on the same chip.

## 2.1.4 Intellectual Property origin

In modern high technology economies access to Intellectual Property (IP) is crucial. When IP is concentrated in a region, such as it is with computing technologies, the potential exists that access to this IP may be precarious, or simply expensive. It is economically important for large regions to have access to multiple sources of IP (for competitive pricing) and to try to generate their own critical IP (to guarantee access). The consequences of this can be seen in China with the development of their own line of x86 compatible CPUs, in Japan with their investment in ARM technologies and the EU with the European Processor Initiative (EPI).

# 2.2 Notable Hardware Developments

In previous iterations of this deliverable (see [2, 3, 4]), we have in this section provided lists of available hardware and platforms that are, or will be, accessible to E-CAM developers. In the current iteration we no longer try to be exhaustive but focus more on particular developments that may be of significant potential impact to our user community.

We continue to add increasing importance to Section 3 which attempts to identify software solutions that may help insulate E-CAM developers from an increasingly diverse computing environment over which they do not ultimately have a lot of control.

#### 2.2.1 European Processor Initiative

The EPI is a project currently implemented under the first stage of the Framework Partnership Agreement signed by the Consortium with the European Commission, whose aim is to design and implement a roadmap for a new family of low-power European processors for extreme scale computing, High Performance Data Analysis (HPDA) and a range of emerging applications.

The initial focus will be placed on integration of technologies to allow the creation of a General Purpose Processor (GPP), over multiple generations with increasing levels of IP generation. The first generation of the GPP, codenamed "Rhea", will have a design that incorporates Arm, RISC-V, high bandwidth memory, and other technologies in a multitile package. It had been scheduled for release in 2021, intended to be used in the first European exascale prototype systems. The second generation architecture, code-named "Cronos", is scheduled for 2022-2023 and expected to be included into European production exascale systems.

The ARM tiles will act as the host processor for other auxiliary processors, which includes Multi-Purpose Processing Array (MPPA) technology (generally used to speed up embedded computing functions), embedded FPGA (that can be used as a reconfigurable accelerator or to implement dynamic hardware modifications), and a custom HPC accelerator architecture that will be developed by EPI.

The accelerator stream will develop and demonstrate fully European processor IPs based on the RISC-V Instruction Set Architecture, providing power efficient and high throughput accelerator tiles within the General Purpose Processor (GPP) chip. Using RISC-V allows leveraging open source resources at hardware architecture level and software level, as well as ensuring independence from non-European patented computing technologies.

#### 2.2.2 Intel

Intel is attempting to create serious competition for (the currently dominant) NVIDIA in the accelerator space with the recently announced Intel X<sup>e</sup> architecture, which will be used in new integrated and discrete Intel GPUs from 2020. The strong selling point is that they can provide an accelerated computing ecosystem to rival CUDA that will be needed for exascale computing.

The X<sup>e</sup> architecture encompasses 3 flavours: X<sup>e</sup>-LP (Low Power), X<sup>e</sup>-HP (High Power) and X<sup>e</sup>-HPC (High Performance Computing). While the first two are more graphics/data centre focused, X<sup>e</sup>-HPC is the most relevant here with its emphasis on raw throughput. X<sup>e</sup> contains both CPU-style SIMD (Single Instruction, Multiple Data) units as well as GPU-like SIMT (Single Instruction, Multiple Threads) units, that can be combined on the same card to maximise performance for particular workloads, e.g. kernels can perform some serial work on the SIMD units of the GPU without having to move these back to the CPU. For the X<sup>e</sup>-HPC design at least, support for double precision floating point computations will be extensive.

See Section 3.2.5 for information on the programming model intended for leveraging these developments.

Moving data in and out of these X<sup>e</sup>-HPC compute units will involve some direct connections between neighbouring units and the use of a new, scalable memory fabric called XeMF that connects to HBM (High Bandwidth Memory) channels. There is also a special high-speed cache for the compute units to call upon.

Intel announced in late 2019 that the first X<sup>e</sup>-HPC GPU will be a design called Ponte Vecchio (PVC). The technology is expected to be the workhorse of the upcoming Aurora A21 exascale system to be installed in Argonne National Laboratory.

## 2.2.3 AMD

While Intel has dominated the HPC processors market for the last decade or so, there is renewed competition from AMD in 2019 with the release of its second generation (Zen 2) EPYC processor called "Rome". It represented the first time that AMD has released a HPC oriented processor with smaller, 7nm transistors ahead of its biggest rival. AMD Rome CPUs have since been deployed on large European supercomputers such as the 26-petaflop Hawk system at HLRS (Stuttgart, Germany) and an upcoming 6.4-petaflop supercomputer at CSC (Finland) to be installed in 2020.

Apart from CPUs, AMD has also announced aggressive plans to compete with Intel and NVIDIA in the accelerator space. It has announced in early 2020 a GPU architecture called CDNA, which is more compute focused compared to the company's gaming GPUs. AMD plans to couple the CPU and GPUs together, using its Infinity architecture, into one unified data model so data movement will not have to be explicitly managed by the programmer.

Rome will be followed by the third generation (Zen 3) "Milan" processor, expected late 2020 and the Zen 4 based "Genoa" processor, expected in 2022. These AMD EPYC CPUs and GPUs will power 2 upcoming exascale systems in the U.S. – the 1.5-exaflop Frontier supercomputer at Oak Ridge National Laboratory in 2021 and the 2-exaflop El Capitan supercomputer at Lawrence Livermore National Laboratory (LLNL) that serves the National Nuclear Security Administration (NNSA) in 2023.

## 2.2.4 NVIDIA

The HPC accelerator space has been dominated by NVIDIA GPUs for many years. While both Intel and AMD are planning competition in this area of the HPC market, NVIDIA benefits from an established hardware and software ecosystem, including rich support for applications and the popular CUDA programming framework optimised for its GPUs. NVIDIA GPUs are also widely used for AI and deep learning workflows.

NVidia has just released the new GPU architecture, Ampere, which contains a higher mix of CUDA cores (for compute workloads), Tensor Cores (for AI and Deep Learning workloads, and now even in full FP32) and RT Cores (a relatively new feature aimed at ray tracing and related workloads). The new card allows more than 1.5x speedup, compared to previous Volta generation, on most of the Molecular Dynamic solvers like LAMMPS, NAMD and GROMACS widely used in the E-CAM community. It is based on a TSMC 7nm N7 technology and provides 1.5TByte of memory bandwith, i.e. 1.7x the previous generation which explains the speedup mentioned, since most of the solvers are memory bandwidth bound. On the half precision side, it achieves 78 TFLOPS in FP16 which could enable new algorithms based on mixed and reduced precision.

ATOS has just announced that the first supercomputer with A100 GPU card will be available in the next Q2 of 2020 at Julich Supercomputer Centre.

#### 2.2.5 ARM

ARM has a different business model compared to Intel and AMD in the server and HPC domain, by developing technology that is licensed to semiconductor companies, i.e. other companies can license complete ARM microarchitectures or obtains an architectural license to new CPU microarchitectures from scratch, while still conforming to the ARM model. The latter has seen the emergence of new, power-efficient processors that have seen increasing adoption in HPC. For example, the ARM-based Cavium ThunderX2 chips from Marvell are used in supercomputing projects at Sandia National Laboratory as well as in CEA, France. Notably, Fujitsu's A64FX ARM CPU will power Japan's next preexascale "Fugaku" supercomputer (the successor to its "K" supercomputer) which will be installed in RIKEN in 2021. As highlighted above, the European Processor Initiative is also planned to adopt ARM technologies in its roadmap, which will use ARM's "Zeus" cores as its general-purpose processor.

Recently ARM announced a partnership with NVidia to quickly build GPU-accelerated Arm-based servers. Not only NVidia, but the full Arm ecosystem partners — including Ampere, Fujitsu and Marvell — will ensure NVidia GPUs also work seamlessly with Arm-based processors.

## 2.2.6 EuroEXA

Field Programmable Gate Arrays (FPGAs) are semiconductor devices that are based around a matrix of configurable logic blocks (CLBs) connected via programmable interconnects. FPGAs can be reprogrammed to desired application or functionality requirements after manufacturing. This feature distinguishes FPGAs from Application Specific Integrated Circuits (ASICs), which are custom manufactured for specific design tasks.

EuroEXA is an EU Funded 20 Million Euro for an ARM+FPGA Exascale Project which will lead Europe towards exascale, together with ExaNeSt, EcoScale and ExaNoDe projects, scaling peak performance to 400 PFLOP in a peak system power envelope of 30MW; over four times the performance at four times the energy efficiency of today's HPC platforms.

## 2.2.7 Complex I/O layers

The recognition of "Big Data" in scientific applications and the complexity of new storage technologies are likely to have a number of impacts in the wider scientific community when it comes to I/O. This is summarised well within "Eurolab4HPC Long-Term Vision on High-Performance Computing (2nd Edition)":

... the POSIX I/O interface to cold data (e.g. Lustre, GPFS, or the limited Hadoop DFS) remains largely agnostic to the I/O optimization opportunities that array-centric computing presents. This simplistic view of I/O for array-centric analyses is challenged by the dramatic changes in hardware and the diverse application and analytics needs in today's large-scale computers: On the hardware front, new storage devices such as SSDs and NVMe not only are much faster than traditional devices, but also provide a different performance profile between sequential and random I/Os. On the application front, scientific applications have become much more versatile in both access patterns and requirements for data collection, analysis, inference and curation. Both call for more flexible and efficient I/O abstractions for manipulating scientific data.

•••

The rapid adoption of new storage media, has shifted the perception on using third-party I/O libraries for data storage and access. A 2014 user survey of the NERSC scientific facility shows that the HDF5 and NetCDF file format libraries are among the most widely used libraries, and have at least as many users as popular numerical libraries, such as BLAS, ScaLAPACK, MKL and fftw [16]. In 2018, 17 out of the 22 projects in the U.S. Department of Energy Exascale Computing Project (ECP) portfolio were using HDF5. These file format libraries present a semantically richer, array-centric data access interface to scientific applications. Using such file format libraries allows applications to navigate through a hierarchical organization of datasets, explore rich metadata about each dataset, choose subsets of an array, perform strided accesses, transform data, make value-based accesses, and automatically compress sparse datasets to save space.

Many research efforts seek to bring richer data management functionality in file format libraries and largely explore three complementary avenues: (1) extending the functionality of file format libraries, (2) developing connectors and (3) automatically migrating data.

Given this analysis, for developers to avail of hardware developments at the I/O level, it would seem prudent for applications to adopt an I/O layer built upon an established and maintained file format library. At this time, it is clear HDF5 should probably be the base layer of whichever library is chosen.

#### 2.2.8 Memory Hierarchy

It is expected that future supercomputers are going to fall into two main categories of memory hierarchy;

- Deep Memory; low speed non-volatile memories may lead to additional levels to close the gap between mass storage and memory.

- Shallow Memory; where main memory may be merged with storage for smaller systems, so the cache, main memory and mass storage might be merged to a single level, providing the system with an improved performance system-wide. It would enable applications to use more non-uniform/highly random data access.

The implications of this are that merging main memory and mass storage allows the quicker start of applications, crash recovery, and a reduction in energy consumption. Additional work on security and privacy needs to be incorporated into the design features however.

#### 2.2.9 Feedback for software developers

Extreme computing and AI are currently global issues and key components of global economies and global security. It is not surprising then to see competition increase in such a huge (and growing) market. The unfortunate end result for a scientific developer is that there is no developer ecosystem that can leverage all of this diverse hardware.

Several approaches have been developed to exploit the full power of accelerators: from parallel computing platform and application programming interface specific for NVIDIA GPUs, like CUDA 10.0, to the latest version of OpenMP 5.0 which contains directives to offload computational work from the CPU to the GPU. While CUDA currently is likely to achieve best performance from an NVIDIA device, OpenMP allows for better portability of the code across different architectures. Finally, the OpenACC open standard is an intermediate between the two, more similar to OpenMP than CUDA, but allowing better usage of the GPU. Developers are strongly advised to look into these language paradigms.

Moreover, it is fundamental to consider there the several issues linked to hybrid architectures. In the case of a GPU we have CPU-GPU and GPU-GPU bandwidth communication, direct access through Unified Virtual Addressing and the presence of new APIs for programming (such as Tensor Core multiplications specifically designed for deep learning algorithms).

At this stage, accelerator programming is quite mainstream and there are many training courses available online, see for example the NVIDIA education site for material related to CUDA and OpenACC. Material for OpenMP is more limited, but as an increasing number of compilers begin to support the OpenMP 5.0 standard, we expect the amount of such material to grow (see this presentation on performance of the Clang OpenMP 4.5 implementation on NVIDIA GPUs for a status report as of 2016). FPGAs use a dataflow based programming model, a programming paradigm that models a program as a directed graph of the data flowing between operations. Despite their high efficiency in performance and power consumption, FPGAs are known for being difficult to program. In the EuroEXA project one of the partners is Maxeler who provide hardware systems that combine conventional CPUs with high performance Dataflow Engines (DFEs) built around Field Programmable Gate Array (FPGA) chip technology. The application design process using Maxeler technologies is described very well by EoCoE in a June 2018 webinar on FPGA computing.

In general, the current FPGA environment is similar to the GPU space some years ago in that HPC is not the primary market but could be a significant one. There is no common standard being championed to improve their programmability, so choosing one or the other vendor locks the user into a particular development platform (to some extent).

Overall, the hardware is growing in diversity and unfortunately there is no API that is going to allow you to program for all of them. Each hardware combination is likely to have different capabilities, and different performance characteristics and bottlenecks. As a result, an optimisation for one combination of hardware components may not be possible on another, or may indeed be a pessimization. It's for this reason that we focus on viable "middle-men" in Section 3.

With respect to I/O, we must note that the hardware complexity at this level is also going to increase significantly and will become a burden if developers attempt to engage with this directly. The advice would be to avoid creating an issue of this topic through the use of a file-format library in your I/O layer. In particular, it would be advisable that your I/O layer is built (either directly or indirectly) upon HDF5 whose adoption is widespread and is undergoing significant and continuous development.

# 2.3 Extreme-scale resources at the European level

#### 2.3.1 EuroHPC

As part of the EU HPC policy, a multi-government agreement (20 as of June 2018) has been signed to acquire and deploy, by 2022/2023, a pan-European integrated exascale supercomputing infrastructure: EuroHPC. It will address three urgent needs:

- to procure and deploy in Europe in competitive timeframes a world-class pre-exascale HPC infrastructure;

- to make it available to public and private users for developing leading scientific and industrial applications;

- to support the timely development of the next generation European HPC technologies and their integration into exascale systems in competitive timeframes with respect to our world competitors.

With a total budget of approximately EUR 1 billion, the Joint Undertaking will function until 2026. The Joint Undertaking aims by 2023 to deploy at least one exascale system based on European technology and in June 2019 selected the Hosting Entities for Precursors to Exascale Supercomputers. The decision was taken in the meeting of the Governing Board of the EuroHPC Joint Undertaking, in Luxembourg, on June 7 2019, where three different hosting sites for pre-exascale systems were selected: Bologna (Italy), Barcelona (Spain) and Kajaani (Finland). The call for Hosting Entities for Exascale Supercomputers will also soon be announced.

E-CAM is participating in the EuroHPC Working Group on User Requirements, submitting a position paper to the Group in June 2018 and attending an associated workshop.

#### 2.3.2 Current PRACE Resources

As far as the Partnership for Advanced Computing in Europe (PRACE) initiative is concerned, the complete list of available resources are shown in Figure 2.

Access to PRACE resources can be obtained by application to the PRACE calls.

Moreover, the Distributed European Computing Initiative (DECI) is designed for projects requiring access to resources not currently available in the PI's own country but where those projects do not require resources on the very largest (Tier-0) European Supercomputers or very large allocations of CPU. To obtain resources from the DECI program, applications should be made via the DECI calls.

## 2.3.3 Feedback for software developers

While it is still too early to know the hardware technology content of the EuroHPC, the technologies described already are very likely to feature in the precursors. Practically speaking one must then consider the software implementation implications, something that is covered in some detail in Section 3.2.

|             |                        | НАШК                        | JOLIOT-<br>CURIE<br>AMD      | JOLIOT-<br>CURIE<br>SKL                     | JOLIOT-<br>CURIE<br>KNL                                        | JUWELS                                         | SuperMUC<br>NG                                         | MARCONI<br>100                                        | MARCONI<br>SKL                              | Mare<br>Nostrum4                            | Piz Daint                                           |

|-------------|------------------------|-----------------------------|------------------------------|---------------------------------------------|----------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|---------------------------------------------|-----------------------------------------------------|

| System Type |                        | HPE                         | Bull<br>Sequana<br>X1000     | Bull<br>Sequana<br>X1000                    | Bull<br>Sequana<br>X1000                                       | Bull<br>Sequana<br>X1000                       | Lenovo                                                 | Lenovo<br>System<br>NeXtScale                         | Lenovo<br>System<br>NeXtScale               | Lenovo                                      | Hybrid<br>Cray xC50                                 |

|             | Processor<br>Type      | AMD EPYC<br>Rome            | AMD EPYC<br>Rome @<br>2.6GHz | Intel Xeon<br>Platinum<br>8168 @<br>2.7 GHz | Intel<br>(Knights<br>Landing)<br>Xeon Phi<br>7250 @<br>1.4 GHz | Intel<br>Xeon<br>Platinum<br>8168 @<br>2.7 GHz | Intel Skylake<br>Xeon<br>Platinum<br>8174 @ 3.1<br>GHz | IBM<br>POWER9<br>AC922 @ 3.1<br>GHz                   | Intel Xeon<br>Platinum<br>8160 @ 2.1<br>GHz | Intel Xeon<br>Platinum<br>8160 @ 2.1<br>GHz | Intel Xeon<br>E5-2690 v3<br>@ 2.6 GHz<br>(12 cores) |

|             | Total # nodes          | 5,000                       | 2,292                        | 1,656                                       | 828                                                            | 2,511                                          | 6,480                                                  | 980                                                   | 3188                                        | 3,456                                       | 5,704                                               |

| Compute     | Total # cores          | 640,000                     | 293,376                      | 79,488                                      | 56,304                                                         | 120,528                                        | 311,040                                                | 31,360                                                | 153,024                                     | 165,888                                     | 68,448                                              |

| Ŭ           | #<br>accelerators      | n.a.                        | n.a.                         | n.a.                                        | n.a.                                                           | n.a.                                           | n.a.                                                   | 4 per node                                            | n.a.                                        | n.a.                                        | 1 per node                                          |

|             | Type of<br>accelerator | n.a.                        | n.a.                         | n.a.                                        | n.a.                                                           | n.a.                                           | n.a.                                                   | NVIDEA<br>Volta V100<br>GPUs,<br>NvLink 2.0,<br>16 GB | n.a.                                        | n.a.                                        | NVIDEA<br>Tesla P100<br>16GB                        |

| Memory      | Memory/<br>Node        | 128 GB                      | 256 GB                       | 192 GB                                      | 96 GB<br>DDR4 + 16<br>GB<br>MCDRAM                             | 96 GB                                          | 96 GB (144<br>nodes with<br>768 GB)                    | 256 GB                                                | 96 GB<br>DDR4 +<br>16 GB<br>MCDRAM          | 96 GB (200<br>nodes with<br>384 GB)         | 64 GB                                               |

| Network     | Network<br>Type        | Infinibad<br>HDR            | Infiniband<br>HDR            | Bull<br>Exascale                            | BULL BXI                                                       | InfiniBand<br>EDR                              | Intel Omni-<br>Path<br>Architecture                    | Intel Omni-<br>Path<br>Architecture                   | Intel Omni-<br>Path<br>Architecture         | Intel Omni-<br>Path<br>Architecture         | Cray Aries                                          |

| Netv        | Connectivity           | 9D<br>Enhanced<br>Hypercube | Dragonfly +                  | Fat Tree                                    | Fat Tree                                                       | Fat Tree                                       | Fat Tree                                               | Fat Tree                                              | Fat Tree                                    | Fat Tree                                    | Dragonfly                                           |

Figure 2: List of PRACE Resources (as of 2020) with associated hardware characteristics.

# 3 Software Needs

While the original scope of this section was intended to collect information from the E-CAM community that could be relayed back to hardware and software vendors, it is clear that the hardware developments described in Section 2 will greatly impact the software development practices of the E-CAM development community. For this reason, we go beyond this original scope and in addition we highlight the language standards, runtime environments, workflows and software tools that can help E-CAM developers to deliver high quality, resilient software for current and next generation machines.

# 3.1 Software needs as collected by the E-CAM Software Survey

The E-CAM Survey of Application Software was created to collect basic information about the software, libraries and applications that are frequently used by people in the extended Centre Européen de Calcul Atomique et Moléculaire (CECAM) community, with a view to trying to develop a support infrastructure for heavily-used software within E-CAM. It includes questions about the application; scientific area; parallelization techniques; the users familiarity with, and capabilities of, the application; the sizes of users typical resource requirements; and finally whether they are a user or developer of the application.

The survey was circulated to our complete set of mailing lists (including industrialists), was distributed to all Extended Software Development Workshop (ESDW) participants in 2017 and remains available on the E-CAM webpage. To date, we have received 160 responses with 67 distinct application codes listed (154 are included in the analysis here). We are conscious that the responses related to the survey may not sufficient to be representative of the entire community since many of the responses are received following direct requests during events held by E-CAM.

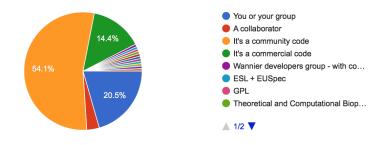

Fig.3 shows that more than 54% of them simply *use* a open-source community code, while about 20% of them are open-source code developers with about 14% of them using a commercial code.

Figure 3: Question: Who develops the software?

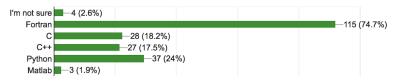

Fig.4 shows that ~75% of the software of the survey is written in Fortran, with about ~36% in C/C++ and a further 24% using Python (or Python bindings).

Figure 4: Question: The Programming Language used by the software.

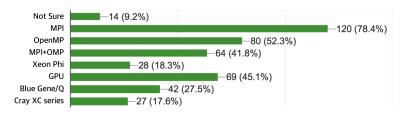

Fig.5 shows that three quarter of the respondees use a code with an MPI implementation and half with an OpenMP implementation. About 40% of them are under Hybrid MPI/OpenMP mode. GPU capabilities are available to 45% of the applications.

Figure 5: Supported (parallel) software capabilities

Fig.6 shows that 89% of respondees get their publication-quality results through the use of resources at HPC centres.

Figure 6: Most common hardware used for generating publication-quality results

Fig.7 shows that almost half them use less than 128 cores for simulation and less than one quarter of them use 1024 cores or beyond. This clearly indicates that only a small subset of respondees have requirements that potentially extend to extreme-scale resources (although the potential use case for High Throughput Computing was not included in the questionnaire and will be added in the next iteration).

Figure 7: Max number of cores used per run

Fig.8 shows that more than 80% of them get their jobs finished within 24 hours (or have restart capabilities in the application).

Figure 8: Max number of hours used per run

While the survey is still not large enough to draw strong conclusions, we can extract some trends with respect to the **softwares needs** of the E-CAM community:

- Most of the users use open-source community codes and don't necessarily have the capacity to maintain/develop them. The needs for commercial codes represent only a small portion of the community.

- Since the majority of the codes included are written with Fortran, any contributions that our community make to these codes will necessarily have to be written in Fortran. However, the development and use of Python bindings becomes increasingly popular. Teaching the community how to use (and create) efficient Python bindings and using Python for non-performance-critical components of their workflow should be very helpful for the community (and also ease any future transition to other programming models).

- MPI, OpenMP, GPU (CUDA/OpenACC) are the main techniques currently used to enable code parallelisation. Training in these techniques, in particular targeting "accelerator" technologies, are needed.

- About 90% of them use HPC centres for producing science. Guiding them to get access to PRACE resources should be very helpful *but* the scalability of their resource requirements will need to be demonstrated. Given that *ensemble* calculations are very common across E-CAM, the inherent scalability of such workflows need to be emphasised to the community.

#### 3.1.1 Feedback for hardware and software vendors

As the survey stands (and the results should be considered limited despite 160 responses), the indications are that the E-CAM community relies heavily on a diverse set of community-developed applications. The most commonly occuring, at present, are GROMACS, QuantumESPRESSO, Yambo, CP2K, CPMD, LAMMPS, SIESTA, OpenMM, DL\_POLY, DL\_MESO and ESPRESSO++. Only one commercial applications have occurred more than 10 times: the VASP code.

There is still a heavy reliance in the community on Fortran, meaning that support for this language will be essential on future systems if people are to be expected to migrate their current workloads there.

The typical production use cases observed in the community do not necessarily require extreme scalability. This is not to say, however, that the community does not require extreme-scale resources. Vendors should be wary that ensemble calculations are an important part of the workflow across the E-CAM community and that this has potential cost implications for resources suitable to this case (for example, this may significantly impact the design of cost-effective network topologies for E-CAM workloads).

There are many cases where E-CAM developers are interfacing at a relatively abstract level with community codes. Therefore, the appetite for novel technologies is typically reliant on an implementation (and sufficient documentation) within these codes. This is both an opportunity and a burden: a subset of community applications ported to novel technologies may bring large user communities to such resources *but* such applications are so feature-rich (which usually implies monolithic) that this may be exceedingly difficult to implement satisfactorily in practice.

# 3.2 Programming Paradigms

#### 3.2.1 C++17

C++17 is the most recent revision of the ISO/IEC standard for the C++ programming language, published in December 2017.

The previous C++ versions show very limited parallel processing capabilities when using multi/many core architectures. This situation changes with the C++17, in which the parallelised version of Standard Template Library is included. The STL is a software library for C++ programming which has 4 components: Algorithms, Containers, Functors and Iterators. "Parallel STL advances the evolution of C++, adding vectorization and parallelization capabilities without resorting to nonstandard or proprietary extensions, and leading to code modernization and the development of new applications on modern architectures."[5]

A multi-threading programming model for C++ is supported since C++11.

It has been noted by the creator of C++, Bjarne Stroustrup, that the continued introduction of expert-level features into C++ may drive away newcomers and he has helped write a set of guidelines to help people adopt modern C++.

E-CAM is very aware of the parallelism potential of C++17 and hosted a dedicated event to promote the use of C++17 within E-CAM in Barcelona in the first quarter of 2017.

#### 3.2.2 Fortran 2018

Fortran 2018 is a significant revision of Fortran 2008 (which was when Fortran became a Partioned Global Address Space (PGAS) language with the introduction of coarrays). The revisions mostly target additional parallelisation features and increased interoperability with C and was released on November 28, 2018.

Most Fortran-based software E-CAM sees in practice is implemented in Fortran 95 and there appears to be little awareness of the parallel features of the latest Fortran standards. E-CAM has considered organising a workshop that addresses this lack of awareness (similar to the "Software Engineering and Parallel Programming in Modern Fortran" held at the Cranfield University), though initial demand for such an initiative has not been strong within the community. PRACE do offer similar courses, such as Advanced Fortran Programming at E-CAM partner CSC, and we currently direct interested parties to these courses.

It should be noted that low awareness of modern features may be due to the fact that compiler support for the latest Fortran standards is limited. This is most likely due to the fact that Fortran is not widely used outside of the scientific research (limiting its commercial scope), however this will hopefully change with the LLVM Flang Fortran compiler which uses Fortran 2018 as it's reference for implementation.

## 3.2.3 The (potential) role of Python

Given that it is an interpreted language (i.e., it is only compiled at runtime), Python is usually not discussed much in the HPC space since there is limited scope for control over many factors that influence performance. Where we are observing a lot of growth is where applications are being written in languages like C++ under the hood but are intended to be primarily used via their Python interfaces (as is common in many deep learning frameworks). Examples of this in the E-CAM space would be ESPResSo++, which was one of the applications featured in E-CAM, and PyLAMMPS, the Python interface to LAMMPS (which is preferred as an interface by a significant number of users and developers leveraging LAMMPS).

We also would like to make developers aware of highly sophisticated Python libraries that are extremely useful for HTC. One of these libraries, Dask, is leveraged by E-CAM within it's own HTC library jobqueue\_features which targets MPI workloads.

One should also be aware of the possibilities provided by numba, which is an open source JIT (*just in time*) compiler that translates a subset of Python and NumPy code into fast machine code. numba even supports CUDA GPU programming by directly compiling a restricted subset of Python code into CUDA kernels and device functions following the CUDA execution model.

This is a valuable, and user friendly, development model that allows users to leverage Python for fast prototyping while maintaining the potential for high performance application codes.

As of January 1st, 2020, Python 2 is no longer being maintained. For any Python 2 users, the official porting guide has advice for running Python 2 code in Python 3.

## 3.2.4 Open Standards

We describe here some of the open standards that are most likely to be leveraged on next generation HPC resources.

#### MPI

Now more than 25 years old, Message Passing Interface (MPI) is still with us and remains the de facto standard for internode communication (though it is not the only option, alternatives such as GASNet exist). MPI-3.1 was approved by the MPI Forum on June 4, 2015. It was mainly an errata release for MPI 3.0 which included some important enhancements to MPI:

- Nonblocking collectives

- Sparse and scalable irregular collectives

- Enhancements to one-sided communication (very important for extreme scalability)

- Shared memory extensions (on clusters of SMP nodes)

- Fortran interface

Maintaining awareness of the scope of past and future updates to the MPI standard is important since it is the latest features that target the latest architectural developments.

## OpenMP

OpenMP is also 20 years old and remains the most portable option for on-node workloads. The standard has introduced new features to deal with increasing node-level heterogeneity (device offloading, such as for the GPU, in particular) and varied workloads (task level parallelism).

From GCC 6.1, OpenMP 4.5 is fully supported for C and C++ (with Fortran support coming in the GCC 7 series). The level of OpenMP support among other compilers varies significantly.

There is partial support for OpenMP 5.0 (released in 2018) from GCC 9.1, the Cray compilers from CCE 9.0 (via Clang/LLVM) and from version 19.1 of the Intel compilers. OpenMP 4.5 is fully supported by Clang/LLVM with the features of OpenMP 5.0 under active and heavy development.

#### OpenACC

OpenACC (for open accelerators) is a programming standard for parallel computing developed by Cray, CAPS, Nvidia and PGI. The standard is designed to simplify parallel programming of heterogeneous CPU/GPU systems. Since the paradigm is very similar to the latest OpenMP specs, a future merger into OpenMP is not unlikely. Moreover, the latest PGI compiler implements latest C++17 features and allows to offload workload to NVidia GPUs in pure C++ language, as well as mixing with OpenACC and CUDA directives.

It should be noted that CUDA (with the nvcc compiler) is still the most commonly used (and highest performing) library for programming NVIDIA GPUs.

## OpenCL

Open Computing Language (OpenCL) is a framework for writing programs that execute across heterogeneous platforms consisting of central processing units (CPUs), graphics processing units (GPUs), digital signal processors (DSPs), field-programmable gate arrays (FPGAs) and other processors or hardware accelerators. If you want to be portable beyond Nvidia and AMD GPUs the only option is OpenCL. Intel used to support the GPUs with OpenMP target directive, but recently dropped this.

OpenCL 2.2 brings the OpenCL C++ kernel language into the core specification for significantly enhanced parallel programming productivity. OpenCL's bad reputation is at least in part due to its verbose C host API. Its C++ host API on the other hand is quite readable.

When releasing OpenCL version 2.2, the Khronos Group announced that OpenCL would be merging into Vulkan (which targets high-performance realtime 3D graphics applications) in the future, leaving some uncertainty as to how this may affect the HPC space.

What is interesting to note is the progress of SYCL (also by the Khronos Group, SYCL 1.2.1 revision 5 is now the latest release as of April 18, 2019, is based on OpenCL 1.2) which is a royalty-free, cross-platform abstraction layer that builds on the underlying concepts, portability and efficiency of OpenCL that enables code for heterogeneous processors to be written in a "single-source" style using completely standard C++. SYCL includes templates and generic lambda functions to enable higher-level application software to be cleanly coded with optimized acceleration of kernel code across the extensive range of shipped OpenCL 1.2 implementations. Developers program at a higher level than OpenCL C or C++, but always have access to lower-level code through seamless integration with OpenCL, C/C++libraries, and frameworks such as OpenCV or OpenMP.

## HIP

Connected to the announcement of the Frontier exascale system, AMD has decided to create a new solution for programming their GPU: Heterogeneous-compute Interface for Portability, or HIP, is a new C++ runtime API which allows developers to create portable applications that can run on AMD and other GPU's.

Robustness and performance portability testing are still ongoing, but it offers a very similar interface to the CUDA language allowing to easily the conversion of a CUDA code into HIP.

# 3.2.5 Vendor Specific Libraries

## Intel

The new specification, oneAPI supports direct programming and API programming, and will deliver a unified language and libraries that offer full native code performance across a range of hardware, including CPUs, GPUs, FPGAs and AI accelerators. At the core of the oneAPI specification is DPC++, an open, cross-architecture language built upon the ISO C++ and Khronos SYCL standards. oneAPI provides libraries for compute and data intensive domains. They include deep learning, scientific computing, video analytics, and media processing.

It is interesting to note what the Eurolab4HPC Long-Term Vision on High-Performance Computing (2nd Edition) had to say about oneAPI:

oneAPI is based on the SyCL approach, using c++ templates to have a 3-way compilation, allowing for automatic host, accelerator and interface code generation. It is advancing in the direction of programmerguided parallelization, but it is still leaving too many details to the programmer, like manually defining the interfaces between the host and the accelerator. In this way, the programmer is required to indicate the parameters that will be need to be copied to the accelerator. This is still low level programming, compared to higher level programming models like OpenMP, where the interface definition between host and accelerator code is made by the compiler, given the shared/private/firstprivate/map clauses using in the compiler directives.

## AMD

The resurgence of AMD has led to the development of numerical libraries that are specifically tuned for the AMD EPYC processor family. These AMD Optimising CPU Libraries (AOCL) have a simple interface to take advantage of the latest hardware innovations. The tuned implementations of industry standard math libraries enable fast development of scientific and high-performance computing projects. These libraries include;

• AMD BLIS

- AMD FFTW

- AMD LibM

- AMD libFLAME

- AMD ScaLAPACK

The most recent, AMD ScaLAPACK is integrated with optimised versions of BLIS and libFLAME libraries that enables high performance dense linear algebra operations and easy linking.

BLIS is a portable software framework for instantiating high-performance BLAS-like dense linear algebra libraries. The framework has been designed to isolate essential kernels of computation that when optimised enable the optimised implementations of most is its commonly used and computationally intensive operations. Select kernels have been optimised for the AMD EPYC processor family, and have been carried out for single and double precision routines.

On the GPU side, AMD has introduced the ROCm platform, the first open-source HPC/Hyperscale-class platform for GPU computing that's also programming-language independent. Built for scale, supporting multi-GPU computing in and out of server-node communication through RDMA.

Connected to the announcement of the Frontier exascale system, AMD has decided to create a new solution for programming their GPU: Heterogeneous-compute Interface for Portability, or HIP, is a new C++ runtime API which allows developers to create portable applications that can run on AMD and other GPU's and falls under the umbrella of ROCm.

Robustness and performance portability testing are still ongoing, but it offers a very similar interface to the CUDA language allowing to easily the conversion of a CUDA code into HIP.

#### ARM

Until recently, the Arm developer/application ecosystem, e.g. OS support, and importantly for HPC tools and libraries required for performance, has been of concern for HPC users. But it has since garnered wide support from OEMs and industry standard partners. Specifically for HPC, there are open source libraries to optimise performance for ARM-based processors, which are also integrated in ARM Allinea Studio that encompasses C/Fortran compilers, performance libraries, as well as "ARM Forge" (consisting of a debugger, profiler and performance analyser).

## 3.2.6 Runtime System Approaches

As noted already, programming paradigm standards are moving forward to adapt to the technologies that we see in the market place. The complexity of the hardware infrastructure (as outline in Section 2) necessarily brings complexity to the implementation of the programming standards.

There are number of programming models that leverage runtime systems under development. They promise to abstract away hardware during the development process, with the proviso that tuning at runtime may be required. Our experience to date with these systems is limited so we simply provide a list of four such systems here (which is certainly not exhaustive) in no particular order:

- HPX, a C++ Standard Library for concurrency and parallelism. The goal of the HPX project is to create a high quality, freely available, open source implementation of ParalleX concepts for conventional and future systems by building a modular and standards conforming runtime system for SMP and distributed application environments. (Most recent release: v1.4.1, February 2020)